本文讲述了AMD UltraScale /UltraScale+ FPGA 原生模式下,异步模式与同步模式的对比及其对时钟设置的影响。

在 UltraScale/UltraScale+ 中引入了 RXTX_BITSLICE。该原语用于捕获和接收 XPIO IOB。建议用户使用 High-Speed SelectIO (HSSIO) Wizard。UG571详细介绍了原语和连接。

例如,在使用源同步时,为什么 HSSIO Wizard 限制用户每个 Bank 只能使用 23 个差分对?在 UltraScale/UltraScale+ 中源同步有什么要求?我该如何判断是否需要使用异步模式,还是可以改用源同步模式?

值得探讨的首要主题是 UltraScale/UltraScale+ 中的源同步,及其对时钟设置的影响。

在 UltraScale/UltraScale+ 中使用 HSSIO 或原生模式时定义源同步

在源同步模式下使用 RXTX_BITSLICE 时,选通/捕获(QBC 或 DBC)时钟会通过半字节间和字节间时钟设置,直接布线至 Bank 中的捕获触发器。半字节间和字节间时钟设置影响范围不超过其所在 Bank。这意味着捕获时钟需以接口速度来工作(1 Gb/s 捕获条件下,工作频率为 500 MHz),并且它具有已知的相位对齐。捕获时钟可采用边沿对齐或中心对齐与数据对齐。

存储器接口中的选通(通常称之为 DQS)会按数据速率随数据一起发射,并且通常并不会连续发射,它用于在接收侧捕获数据。在 HSSIO/原生模式下,选通是按数据速率与数据一起发射的,并且不一定是连续的。

PLL 的输入来自 GC 管脚,如果位于 _QBC_GC 管脚上并且是连续时钟,则可与捕获时钟/选通共享。Bank 的 PLL 会对含专用输出 CLKOUTPHY 的解串器进行时钟设置,CLKOUTPHY 只能触达其 Bank 内的 BITSLICE & BITSLICE_CONTROL。因此,无法为两个 Bank 的同一个时钟使用源同步。

总结

源同步要求捕获时钟按接口速度来运行,并且已知与数据的相位关系,只能在单个 Bank 内运行。

注释:单个接口可以跨多个 Bank,而 HSSIO 有一个选项,要求每个 Bank 至少一个捕获时钟/选通。

定义异步模式

如果该接口未按接口速率向每个 Bank 发送一个捕获时钟,或者该捕获时钟与接口时钟之间不存在已知的相位关系,则必须将该接口视作为异步。如果存在捕获时钟并且需要跨多个 Bank,则需将其视作为异步。

在某些接口中,会随帧时钟、字时钟或其他并行速率时钟发送数据,这表示会随数据发送一个时钟,但该时钟不可用作为捕获时钟(它需要时钟管理器来进行倍率处理)。

该时钟需视作为异步。 并且,未随数据一起发送时钟的任意接口同样如此。

异步时钟设置

在异步模式 (SERIAL_MODE= TRUE) 中,并不会随选通一起完成 RX 数据的捕获,PLL CLKOUTPHY 用于对捕获触发器进行时钟设置,并且必须存在用于对齐时钟与数据的机制。XAPP1330包含 CDR 逻辑,可搭配 HSSIO Wizard 使用。

如果您的某个接口跨多个 Bank,那么每个 Bank 都需要一个 HSSIO Wizard,并且每个 Wizard 都将使用 PLL 来为每个 Bank 创建一个 CLKOUTPHY。

-

FPGA

+关注

关注

1646文章

22059浏览量

619199 -

amd

+关注

关注

25文章

5592浏览量

136461 -

时钟

+关注

关注

11文章

1903浏览量

133306

原文标题:开发者分享|AMD UltraScale?/UltraScale+? FPGA:异步模式的适用时机及其使用方式

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

同步复位与异步复位,同步释放的对比疑问

怎么理解CC1101的异步串行工作模式?

快速启动是否支持同步读取模式

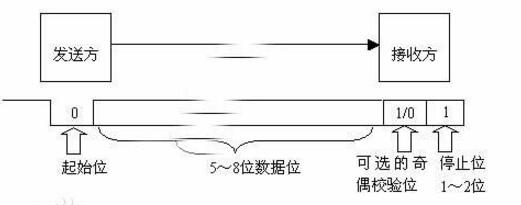

什么是异步转移模式

异步传输模式工作原理简介

FPGA设计中的异步复位同步释放问题

一文看懂异步传输模式atm的特点

AMD FPGA异步模式与同步模式的对比

AMD FPGA异步模式与同步模式的对比

评论