1Versal IO介绍

1.1IO的划分和分布

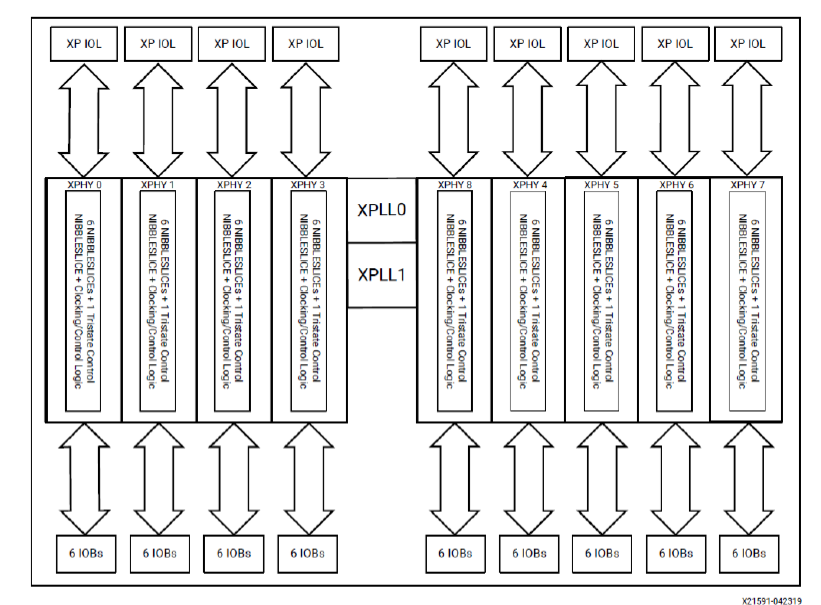

7nm Versal系列相对于16nm Ultrascale plus系列,IO做了升级,U+系列的HPIO在Versal升级为XPIO。Versal系列每一个XPIO bank包含54个IO管脚,其中包含9个nibbles,每个nibbles包含6个IO;每个bank包含2个XPLL、1个DPLL和1个MMCM时钟资源。

1.2IO feature

XPIO支持0.6-1.5v电平,最高速率支持4.22gbps,支持3.2g mipi dphy,支持DDR4/Lpddr4硬核控制器,部分器件支持10g mipi cphy/DDR5/LPDDR5。

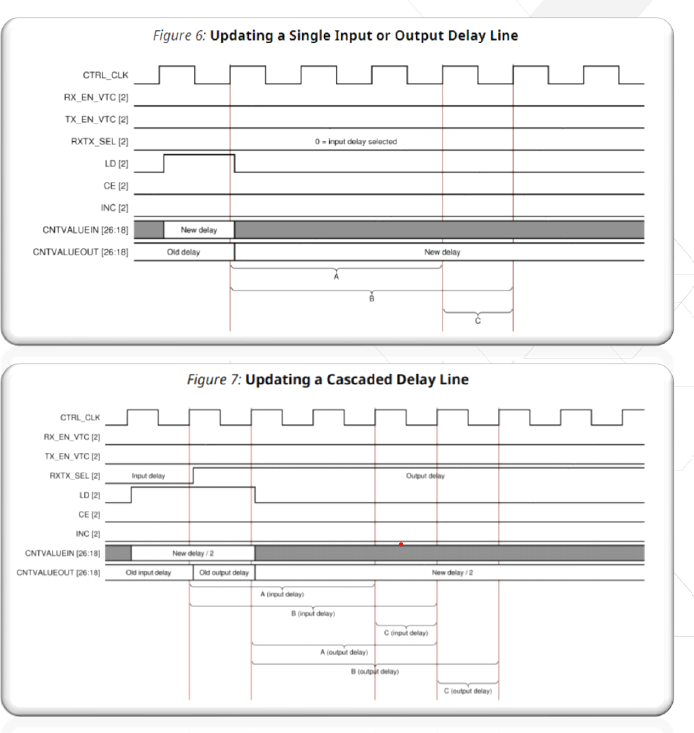

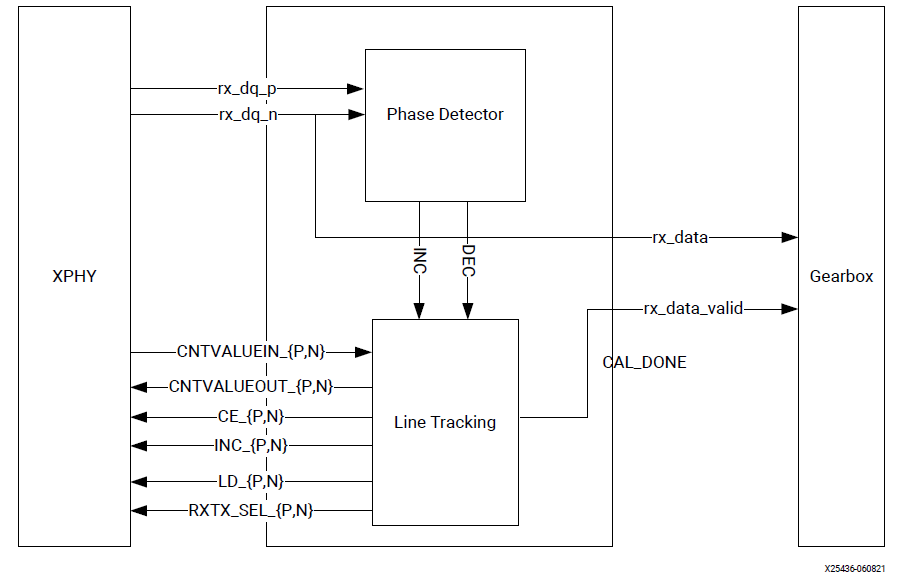

XPHY的IO delays 625 ps(512taps),tap精度约为1.22-4ps,级联后io delay最高达到1250ps;Delay值通过下图所示的XPHY接口完成更新,若需要获取delay信息,建议在变化之后4个时钟周期之后读取更新的值,避开不稳定的状态。

2与U+系列的差异

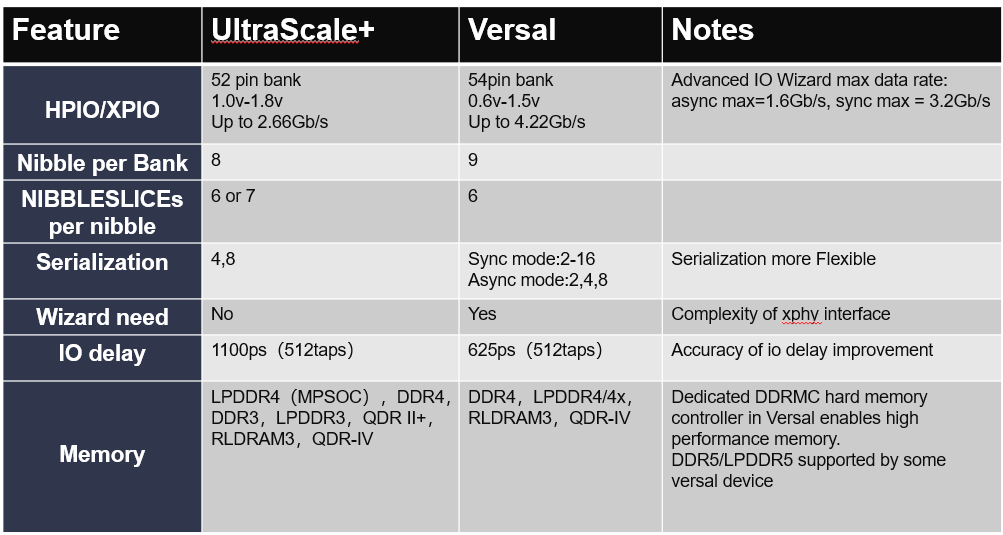

XPIO性能与U+系列select io相比有较大的提升,延迟精度,串化因子等方面都有明显的改善和提升;二者对比如下图所示:

除了IO性能的提升,其他主要的变化包括:

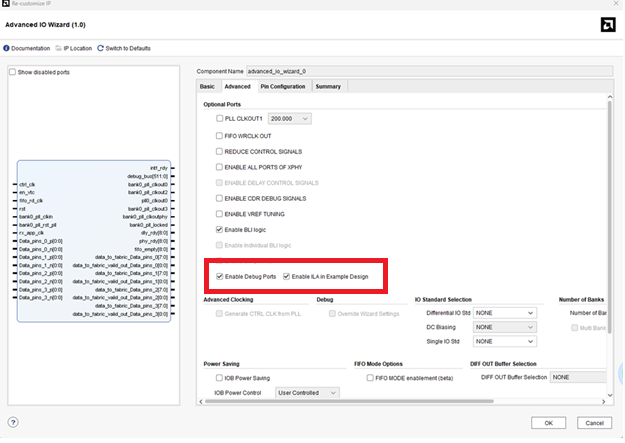

1. IP wizard由High speed SelectIo wizard改为advanced io wizard;

2. Versal系列不再支持hdl only 的设计方式for XPHY XPIO,因为XPHY互联接口非常复杂,因此用户需要基于advanced io wizard完成设计;

3. 支持同步和异步模式,同步模式下最高支持3.2g,异步模式下最高1.6g;

4. 建议通过advanced io planner自动分配io。

3异步模式的设计架构和运行机制

3.1异步模式的架构

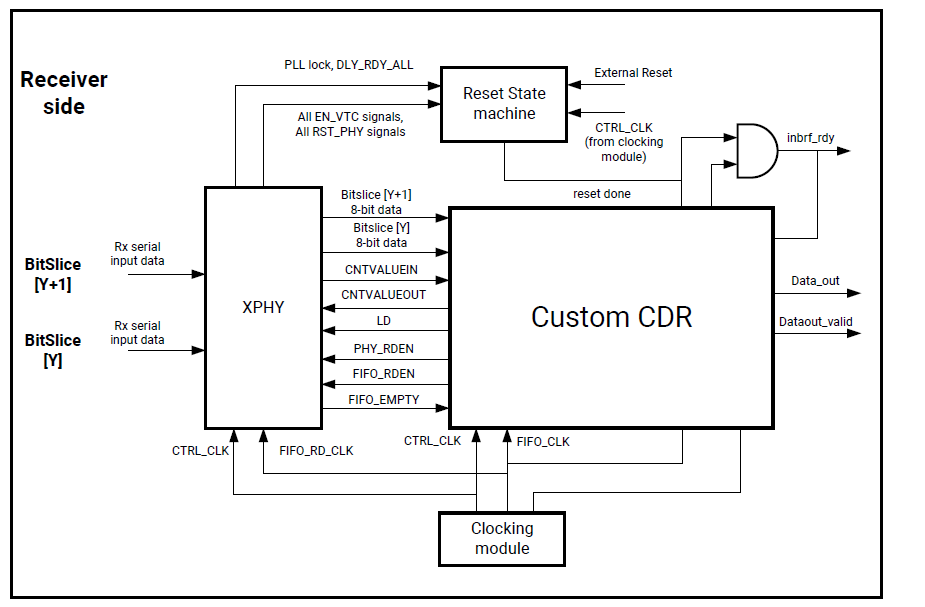

在异步模式下没有随路时钟,需要通过CDR完成数据的恢复和采集。

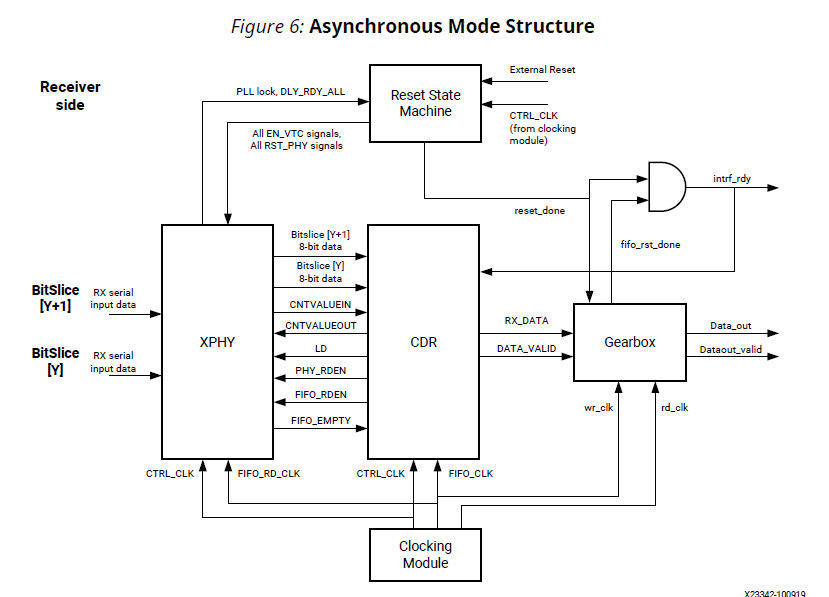

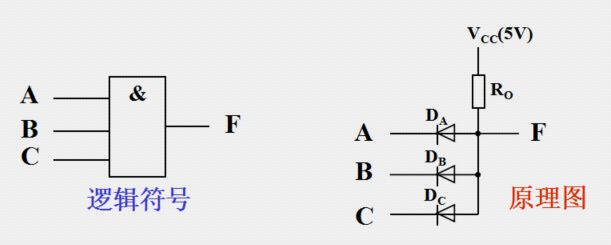

整体架构如下图所示,数据经XPHY接入,在CDR模块完成phase detector,delay line tracking,将找到的delay信息配置到XPHY,当delay不断收敛,CDR模块输出RX_DATA和DATA_VALID给到下一级gearbox模块,在gearbox完成位宽转换并输出有效数据data_out/data_valid。

IP支持两种CDR模式的数据采集:CDR with ppm difference,CDR with Zero ppm;两种模式下CDR的机制没有大的差别,下文以CDR with ppm difference模式为例进行说明。

3.2异步模式下CDR架构

CDR的目的是确保UI采样始终处于异步信号数据的中心位置。UI的采样需要与数据速率相同频率的时钟完成。如SGMII数据速率为1250MBps,则RX和TX锁相环时钟频率应为1250MHz。在CDR with ppm difference情况下,系统要求本地时钟与数据速率原本的时钟ppm差不超过100ppm。

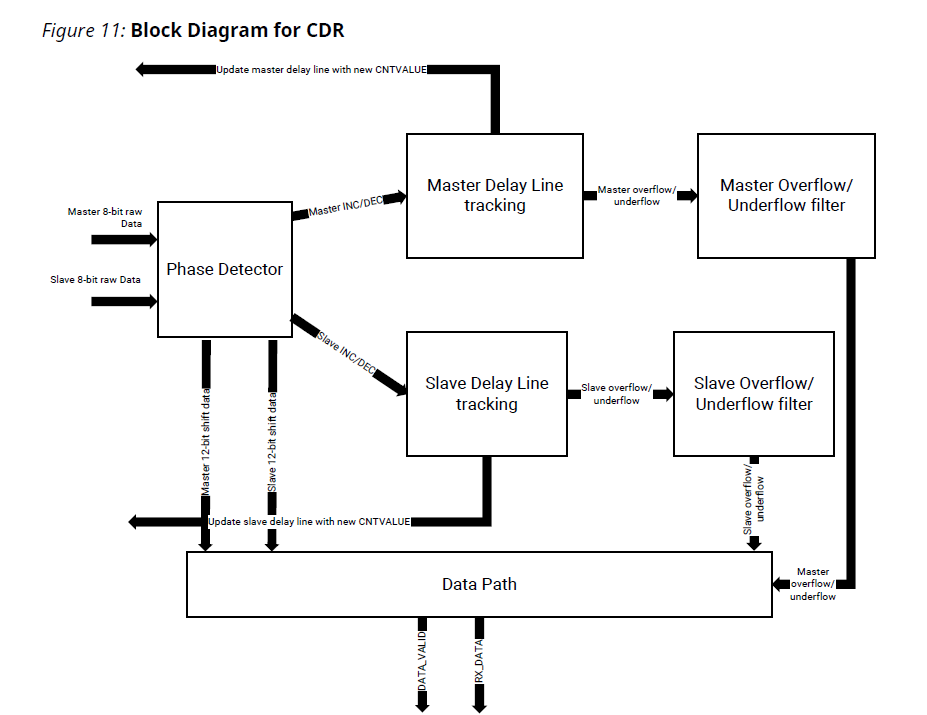

CDR主要包含以下四大模块:

Phase detector

Delay line tracking

Datapath

1 Phase detector

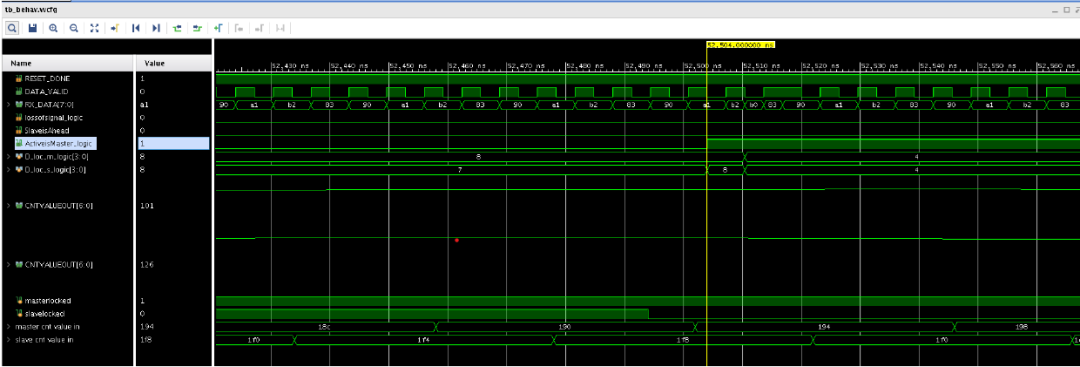

Phase detector拥有master delay line和slave delayline两套延迟线检测机制,两套机制同时工作,互为补充,将最大程度保证CDR能成功锁定。

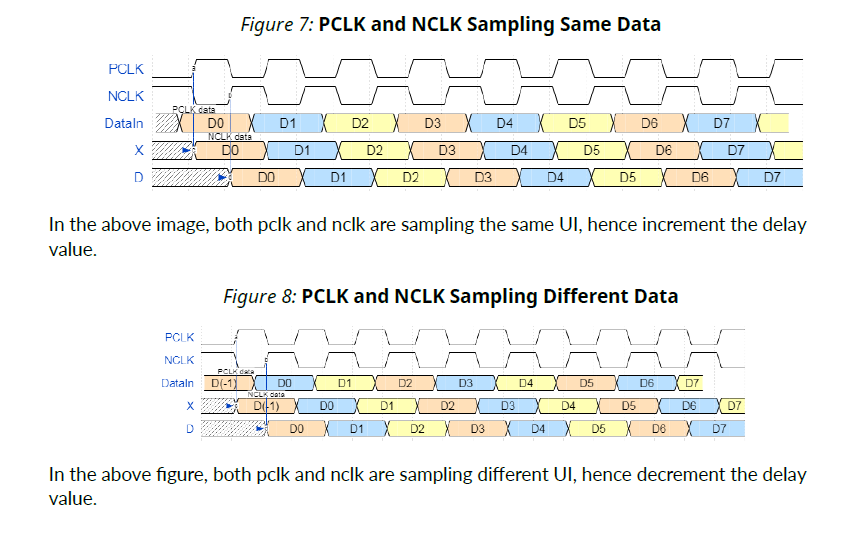

主延迟线和从延迟线对于每个UI,分别取两个样本,送入alexander pangpang鉴相电路,根据获取的数据信息,选择增加或减少延迟。

当差分时钟的p端和n端上升沿采到同一个UI sample,next step增加延时;当p端和n端上升沿采到不同UI sample,next step减少延时。

2 delay line tracking

延迟值在phase dectector模块中不断变化,定期更新到delay line tracking模块中;在delay line tracking模块中,我们会不断跟踪延迟线的变化情况。

经过不断的统计和分析,一旦我们认为从PHY接收到D样本位于UI的中心则当前的延迟线和bitslice被锁定,若一直没有达到UI的中心位置,将会一直调整delay line直到达到边界。到达边界,就会产生overflow和underflow信号。

因此,overflow和underflow在调试中,具有很强的指导意义,我们可以通过overflow和underflow信号,判断CDR是否达到锁定状态。

3 underflow overlow filter

该模块负责正确选择数据并提供给输出。一旦两个延迟线都被锁定,它们自然相隔?个UI,当锁定发生,延迟较少的延迟线,将成为active bitslice,数据将从该延迟线输出,另外一条延迟线将成为备选的monitor bitslice。

当active bitslice发生overflow或underflow时,会自动切换到monitor bitslice获取有效数据,而此时,如果monitor bitslice也发生overflow或underflow,两套机制都无法锁定的情况下,CDR会真正失锁,系统将无法采集到正确的数据。

4 CustomCDR模式

在异步模式下,如果IP自带的CDR无法满足使用需求,客户也可以考虑使能customCDR,参考example design去完成自定义的CDR,取得更大的灵活性;在customCDR模式下,我们完整开放XPHY的延迟配置接口,客户可以根据自己的需求灵活设计自定义的CDR模块。

4advanced io planner

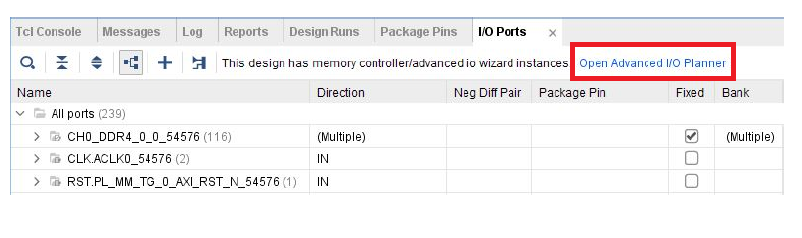

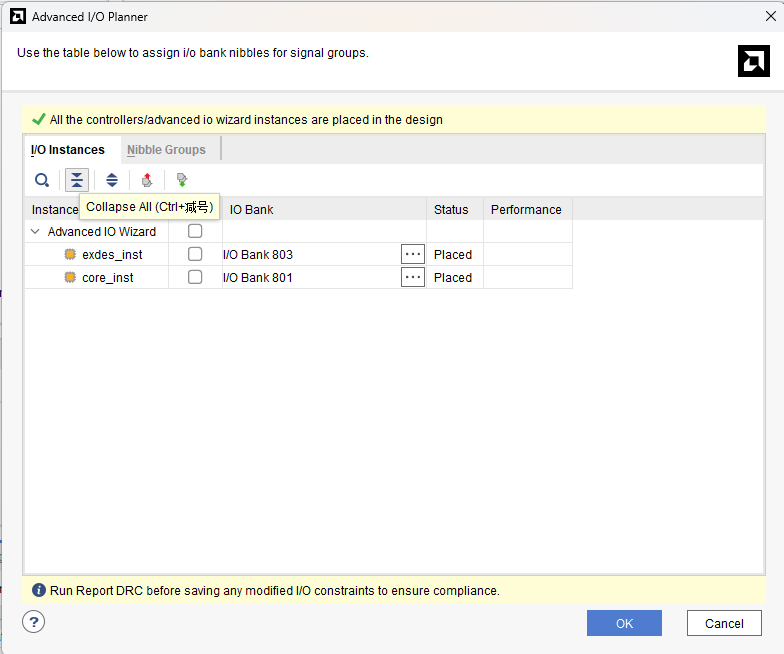

为了更合理的利用XPHY的资源,AMD建议通过advanced io planner来规划IO分配,工具是基于集中式硬件规则尽可能的优化安排的。

工程经过综合之后,点击红色框位置,激活advaned I/O Planner

用户可以选择自动分配,也可以手动进行调整,在IO instances下面工具已经完成自动分配

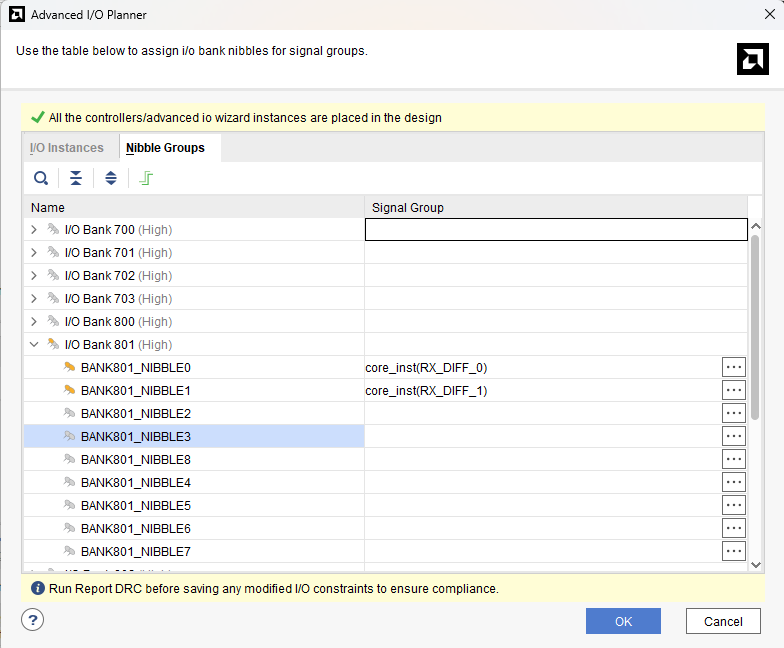

若需要手动调整,在nibble group菜单下面,手动选择你需要放置的nibble

5调试要点

IP调试过程中的几点经验总结如下:

1. advanced io wizard IP无法输出有效数据,data valid不能正常拉高:请检查本地时钟与源端时钟的ppm差,不能大于100ppm;

2. 当采集到的数据出现错误或者位移,可以使能enable debug port,观察是否有出现overflow和underflow的情况,是否存在master delay line和slave delay line切换或者失去锁定的痕迹,帮助确认CDR的锁定状态。

关于安富利

安富利是全球领先的技术分销商和解决方案提供商,在过去一个多世纪里一直秉持初心,致力于满足客户不断变化的需求。通过遍布全球的专业化和区域化业务覆盖,安富利可在产品生命周期的每个阶段为客户和供应商提供支持。安富利能够帮助各种类型的公司适应不断变化的市场环境,在产品开发过程中加快设计和供应速度。安富利在整个技术价值链中处于中心位置,这种独特的地位和视角让其成为了值得信赖的合作伙伴,能够帮助客户解决复杂的设计和供应链难题,从而更快地实现营收。

-

时钟

+关注

关注

11文章

1903浏览量

133387 -

Advanced

+关注

关注

1文章

35浏览量

23546 -

UltraScale

+关注

关注

0文章

123浏览量

31940 -

异步模式

+关注

关注

0文章

2浏览量

700

原文标题:AMD技术干货|Advanced IO wizard异步模式

文章出处:【微信号:AvnetAsia,微信公众号:安富利】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

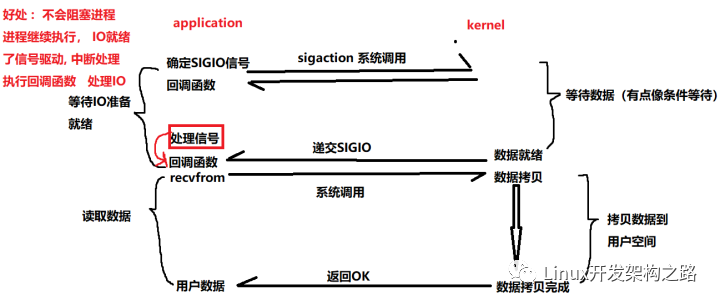

异步IO是什么

《Linux设备驱动开发详解》第9章、Linux设备驱动中的异步通知与异步IO

一文看懂异步传输模式atm的特点

一文详解Advanced IO wizard异步模式

一文详解Advanced IO wizard异步模式

评论